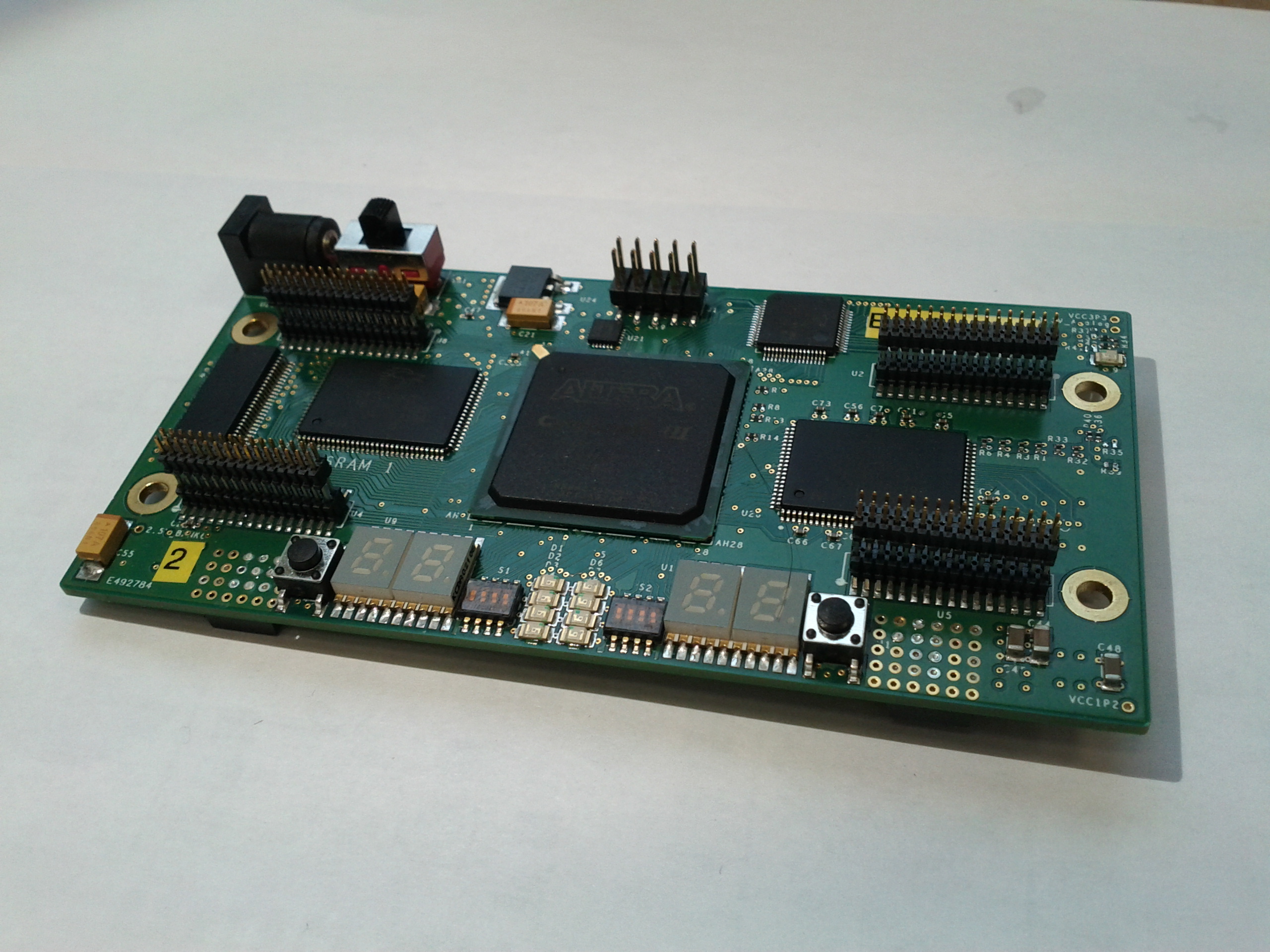

Dream team has developed an architecture of a new smart vision system called BiSeeMos. This smart camera is designed for stereo vision purposes and the implementation of a simple dense stereo vision algorithm. In addition, the architecture has been designed for dedicated parallel algorithms by using a high performance FPGA. This chip provides the user with useful features for vision processing as integrated RAM blocks, embedded multipliers, phase locked loops and plenty of logic elements.

For further information on BiSeeMos architecture including hardware features and design strategies, please read the following article: BiSeeMos. In this article, "Stereo Vision Algorithm Example" is examined in order to demonstrate the efficiency of this platform in real time processing.

More recently two others stereo Smart camera have been done:

-

BiSeeMOS II is lighter the the previous one. The FPGA is EP3C16 with only 1 SRAM Block of 1MWord. Communication link is performed by an embedded USB2.0 chip.

-

BiSeeMOS III is a compromise between the two first ones. It includes a CycloneIII EP3C40 and its size is that of coarsly BiSeeMOS II.